- 雷电竞官网登录

- Power Management

- rayapp

- L竞技

- Sensors

- 灯光

- Custom Mixed-Signal ICs (ASICs)

- Power Conversion

- Power Switching

- Memory

- Silicon IP

- GreenPAK Configurable Mixed-Signal

- 定时

- Communications

- IO-Link.

- Industrial and Automotive ASICs

- Industrial Edge Computing

- IOX扩展模块

- IzoT Commissioning Tool (CT)

- IzoT Net Server

- IzoT SDK 2

- izot shortstack sdk.

- LNS DDE Server

- LON Upgrade

- LonScanner FX Protocol Analyzer

- 智能边缘平台

- SmartServer IoT

- SmartServer IoT™合作伙伴计划

- SmartServer™ IoT Edge Server

- U10 USB网络接口

- U20 USB Network Interface

- U60 DIN USB Expansion Modules

- U60 FT USB网络接口模块

- U70 PL-20 USB Network Interface

- Current Control

- Motor Control

- Display

- Modules

- 长寿计划

- Product Selector

- Document Search

- 雷竞技安卓下载

- Application Solution Diagrams

- Smart Lighting

- Wearables

- Configurable Mixed-signal IC Solutions

- Smart Home

- 家用电器

- 联网

- 汽车

- Industrial

- Smart Meters

- SOC PMIC解决方案

- Communications

- Connected Medical

- Transportation

- Application Solution Diagrams

- Support

- 雷电竞下载app

You are here

Sending a Preset Number of Pulses

Sending a Preset Number of Pulses

通信协议技术

这种技术可以在任何GreenPak中完成。一些GreenPak中的多功能块有助于减少组件计数。

在许多通信协议中,另一个IC发送或接收的设置比特数所必需的。通常,这意味着GreenPak必须跟踪发送或接收的脉冲数。例如,在移位寄存器接收数据中,必须监视比特数以确保预期数据处于正确的寄存器,而不是错误地倾斜或不断地继续移位。

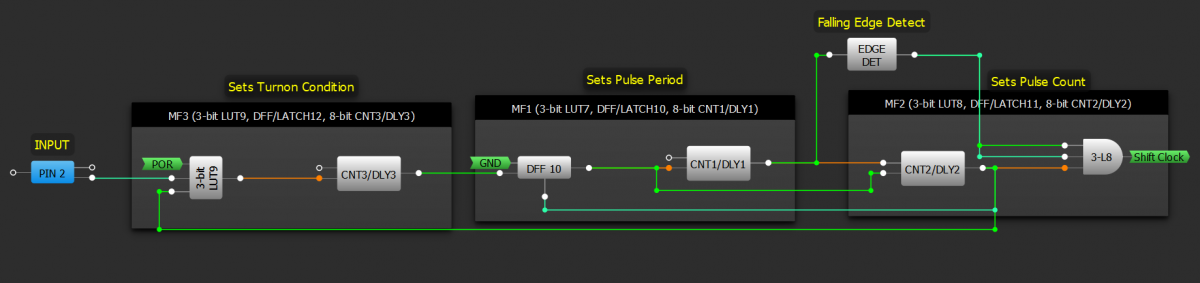

There are many ways to set a predetermined number of pulses in GreenPAK: a scaleable, efficient way is described in this technique. It also has the added benefit of limiting clock skew between the other IC and the GreenPAK by resetting the clock skew after every transaction. Figure 23 shows a pipeline of blocks for creating a preset number of pulses. It consists of: Turnon Condition, Pulse Period, and a Pulse Counter.

图23预设脉冲发生器设计

短扇条件阶段有两个组件:DLY块,以确保最小的活动信号开始脉冲生成,以确保在最后一次事务完成之前未能重新实例化。根据应用,此阶段可能不是必要的。

脉冲周期阶段有两个元素:DFF和计数器。DFF将禁用reset_in.遇到短置条件时计数器的信号。直到脉冲数完成,它将保持低电平。计数器用于设置离散脉冲的时段,并且可以配置为匹配应用程序。

脉冲计数阶段具有下降沿延迟和逻辑门。延迟CLKis connected to the counter in the pulse period stage, which causes it to track the number of pulses. TheDLY INof the delay is connected to the DFF in the Pulse Period stage. This causes the delay to fall low after a set number of pulses, resetting the DFF and halting the shift clock.