- 雷电竞官网登录

- Power Management

- rayapp

- L竞技

- Sensors

- Lighting

- Custom Mixed-Signal ICs (ASICs)

- Power Conversion

- Power Switching

- Memory

- Silicon IP

- GreenPAK Configurable Mixed-Signal

- Timing

- Communications

- IO-Link

- Industrial and Automotive ASICs

- Industrial Edge Computing

- IzoT Commissioning Tool (CT)

- IzoT Net Server

- IzoT SDK 2

- IzoT ShortStack SDK

- LNS DDE Server

- LON Upgrade

- LonScanner FX Protocol Analyzer

- Smart Edge Platform

- SmartServer IoT

- SmartServer IoT™ Partner Program

- SmartServer™ IoT Edge Server

- U10 USB Network Interface

- U20 USB Network Interface

- U60 DIN USB Expansion Modules

- U60 FT USB Network Interface Module

- U70 PL-20 USB Network Interface

- Current Control

- Motor Control

- Display

- Modules

- Longevity Program

- Product Selector

- Document Search

- 雷竞技安卓下载

- Application Solution Diagrams

- Connected Health

- Connected Consumer

- Connected rechargeable E-cigarette

- True Wireless Stereo

- USB Type-C ANC Headset

- Beacon, Tracker, Findable

- DECT Ambient Noise Cancellation (ANC) Headset

- Rechargeable E-Cigarette

- Game Controller

- Feature-rich Rechargeable E-Cigarette

- Rechargeable Game Controller

- Bluetooth ANC Headset

- Toothbrush

- Electric MP3 toothbrush

- Voice RCU

- Animal Tracker / Location Tracker

- POS Terminals

- Wall-to-Battery & Direct Charging

- Smart Home

- Smart Appliances

- Industrial & Infrastructure

- Smart Lighting

- Wearables

- Configurable Mixed-signal IC Solutions

- Smart Home

- Home Appliances

- Networking

- Automotive

- Industrial

- Smart Meters

- SoC PMIC Solutions

- Communications

- Connected Medical

- Transportation

- Application Solution Diagrams

- Support

- 雷电竞下载app

You are here

Parity Bit Generator

Parity Bit Generator

Basic Blocks and Functions

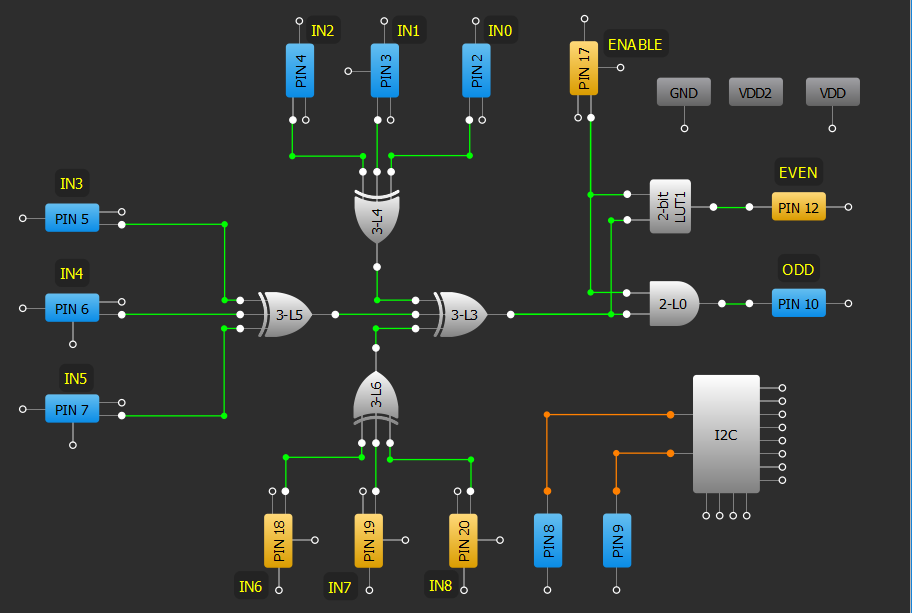

Parity Bit Generators are used to check the integrity of a signal; it is the simplest implementation of a Cyclic Redundancy Check (CRC). Parity Bits are used prior to committing data to an MCU or other control unit to ensure the incoming data hasn’t been corrupted.

Ingredients

- Any GreenPAK

- No other components are needed

GreenPAK Diagram

Design Steps

- Connect input pins using XOR gates usingTechnique: Configuring Standard Logic w/ LUT Macrocells. XOR gates can be used to calculate the running sum of 1’s.

- Add logic for the ENABLE signal.

Resources

GreenPAK Designer files

- Parity Bit Generator GP(5.19 KB)