对于任何低功耗设计,设计者都可以在选择低功耗组件或关闭外围设备的电源之间进行选择。在考虑非易失性闪存的选择时,设计者有相同的这两种选择,每一种都有其优点和缺点,从系统操作、功耗和可靠性的角度来看。然而,还有另一种可用的低功耗解决方案,它具有简化系统设计和提高可靠性的额外好处。

典型的设计使用外部闪存

尽管带有嵌入式闪存的微控制器(MCU)设备越来越多,而且它们可以在多种低功耗模式下运行,但出于扩展的原因,越来越多的系统仍然需要一个外部闪存设备来补充片上闪存。无线(OTA)更新、数据收集、用户档案和其他应用程序都有助于实现这一点。雷竞技安卓下载

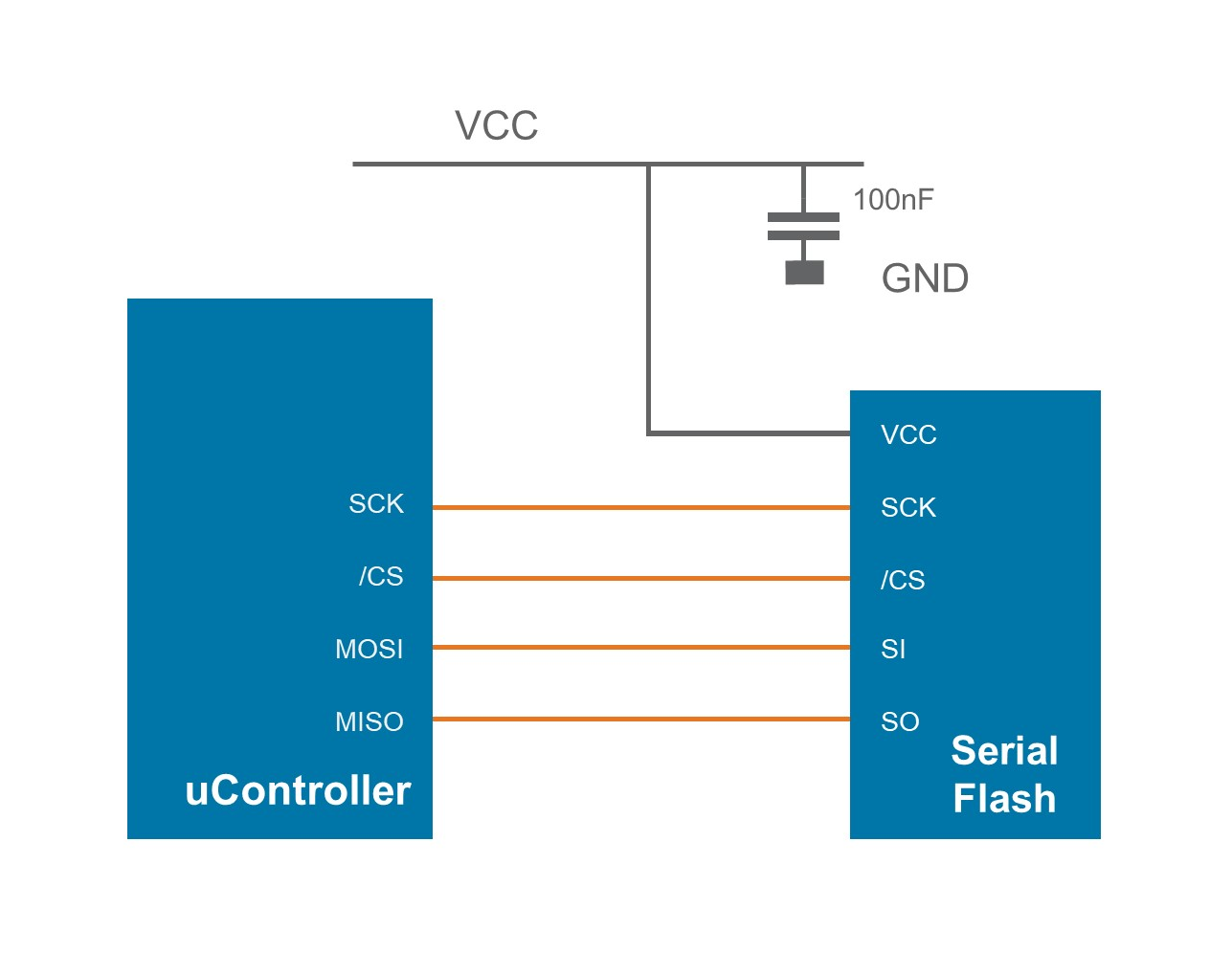

对于许多基本应用,在图1中所示雷竞技安卓下载的典型设计是可接受的解决方案。

图1:使用外部闪存的典型设计

在该解决方案中,功率被连续地提供给闪存设备。当串行闪存片选信号(/ CS)不被肯定和存储器处于待机模式,待机电流通常大约〜10微安到〜的20uA的。此外,还有一个选项,进入命令驱动的深度休眠模式,这更加降低了待机功耗,以典型降至2uA〜 - 〜5UA。

然而,在一些其它系统中,例如能量收集或小电池供电的设备,甚至为2uA可能仍然表示过高的电流消耗值。而且,如果闪光灯不频繁或很少使用访问,为2uA待机长时间可表示在电源和能量储备的过大的漏极 - 降低了整个电池/系统运行寿命。

外接闪光灯,具有简单的电源开关控制电路

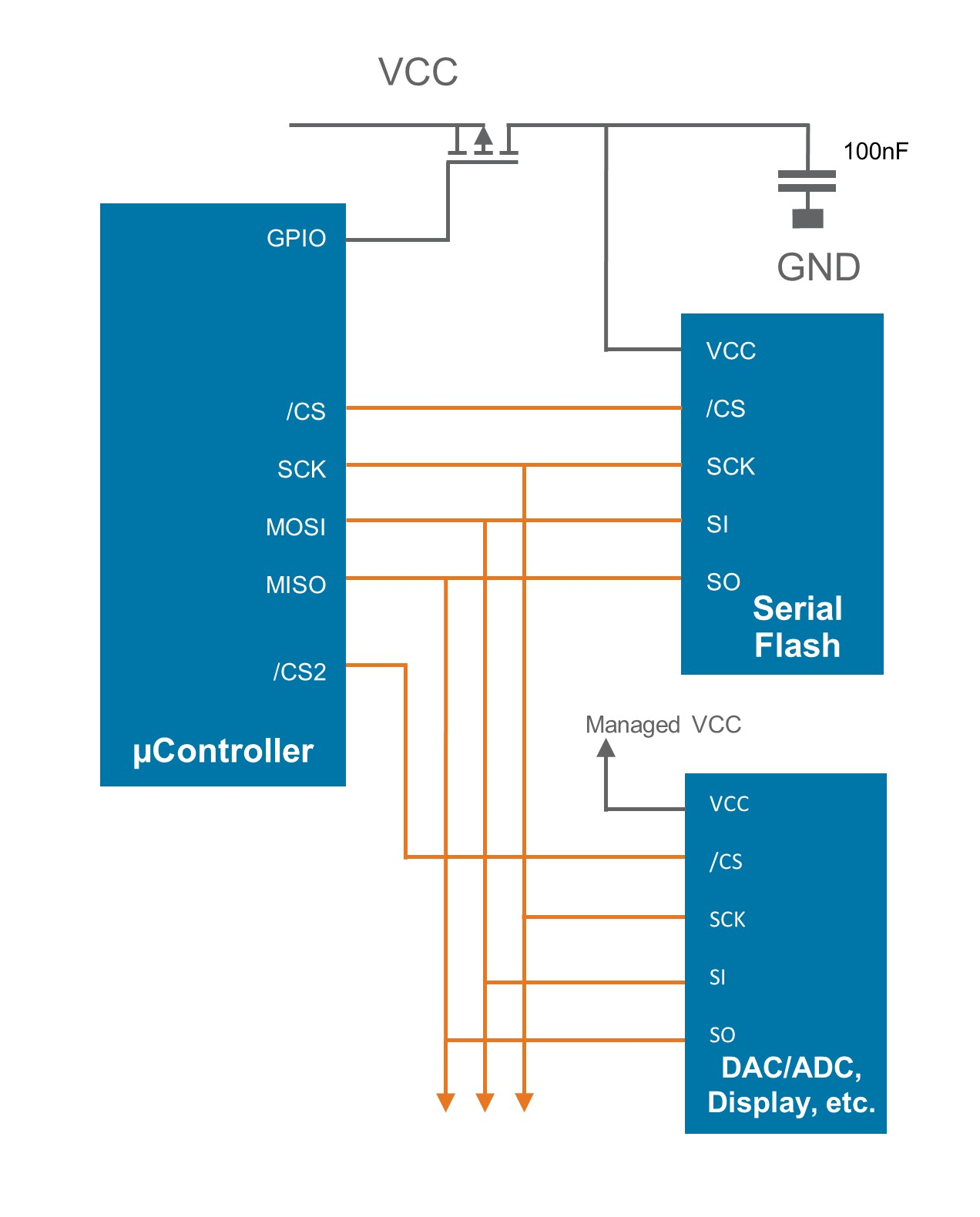

为了提高系统电池的使用寿命,设计者经常实现如图2所示的简单的电源开关控制电路。闪存设备的电源通过一个备用的MCU GPIO引脚在软件控制下管理,以便串行闪存只在需要时供电。

图2:串行闪存外部功率控制电路

不要太舒服了!

MOSFET的完全列入关闭串行存储器VCC将减少内存到零的待机功耗,但MOSFET本身具有潜在的泄漏电流和漏极电流,在某些情况下可达1.5uA,这是只有500nA的更好比高达降至2uA在正常待机内存。

可靠性问题

利用外部FET或LDO与控制栅管理电源向外围设备VCC引脚的溶液变得越来越普遍;然而,这的确也需要额外的MCU GPIO引脚。

更重要的是,当多个外围设备共享公共SPI总线,并且其中各个装置已切换VCC引脚必须小心。

In the configuration shown in Figure 2, if the VCC to the flash is switched off and VCC = 0V, continuing to access the other SPI controlled devices (e.g. DAC/ADC/Display) on the SPI bus will result in bus signals also appearing on the serial flash SPI pins.

在这种情况下,外围SPI总线引脚上的高VCC时,当VCC为flash(或其他设备)是在零将导致I/O保护二极管正偏置,并且设备将潜在地通过I/O引脚本身draw power。这可能会导致短期或长期的可靠性问题和运行问题。

对于那些可能上,而闪光灯关闭动力的任何其他设备,杂散电容也应该让任何引脚上的电压不超过VCC引脚上的电压最小化所有情况。另外,设计师可以考虑更麻烦的解决方案,并添加一个单独的SPI总线为串行存储器,其中VCC可以被关闭。细心的硬件和软件设计和实现能够克服所有这些挑战和问题。然而…

超深掉电(UDPD)选项

...一个更有效的解决方案是由功率控制电路集成到存储设备本身和允许所述主装置(MCU)通过串行闪存SPI命令接口来控制功率模式来实现的。这节省了GPIO引脚用于其他用途。参见图3中的示图。

优点这种解决方案是:

- 它消耗比标准深度掉电功率要少得多。

- 它不需要外部MOSFET。

- 它允许设计人员使用相同的SPI总线为其他外围设备,因此简化了设计。

- 它减轻了可靠性的担忧,因为VCC pin总是连接到VCC,电源是内部控制。

图3:内部管理的串行内存功率控制

并通过SPI命令接口驱动

该解决方案的更多好处是:

- 它节省了一个GPIO pin,将用于开关外部MOSFET或LDO。

- 它简化了软件,因为它消除了多余的MOSFET / LDO控制程序。

- 它提供了一个清洁器PCB设计和降低的物料清单。

Adesto Fusion、FusionHD™(AT25XExxx)和DataFlash™(AT45DBxxxE/F)闪存设备除了待机和深度关机模式外,还提供这种超深度关机模式。待机和深电源关闭模式导致的电流消耗类似或低于其他行业标准闪存设备。

超深度休眠模式需要将静态电流降至低于用于为200nA融合,为100nA的和FusionHD小于降到400nA的数据闪存。

采用超深层关机

实现UDPD模式很简单。详细说明我们在应用注AN111。

结论

选择合适的低功耗内存对于能量收集或小型电池驱动设备来说是一个关键的系统设计因素。理解和管理SPI总线上组件的交互对于提高功能和可靠性也是至关重要的。Adesto的串行闪存解决方案通过考虑内存如何在现实系统中实现,为设计者提供了简化设计、降低风险、提高可靠性和节省外部组件的选项,从而极大地简化了电路并降低了材料成本。

这篇文章是由保罗·希尔,高级市场总监和戈登MacNee,EMEA应用经理撰写雷竞技安卓下载